# VLSI-SoC: From Systems to Silicon

Edited by **Ricardo Reis** Adam Osseiran Hans-Joerg Pfleiderer

# VLSI-SoC: FROM SYSTEMS TO SILICON

#### IFIP – The International Federation for Information Processing

IFIP was founded in 1960 under the auspices of UNESCO, following the First World Computer Congress held in Paris the previous year. An umbrella organization for societies working in information processing, IFIP's aim is two-fold: to support information processing within its member countries and to encourage technology transfer to developing nations. As its mission statement clearly states,

*IFIP's mission is to be the leading, truly international, apolitical organization which encourages and assists in the development, exploitation and application of information technology for the benefit of all people.*

IFIP is a non-profitmaking organization, run almost solely by 2500 volunteers. It operates through a number of technical committees, which organize events and publications. IFIP's events range from an international congress to local seminars, but the most important are:

- The IFIP World Computer Congress, held every second year;

- Open conferences;

- Working conferences.

The flagship event is the IFIP World Computer Congress, at which both invited and contributed papers are presented. Contributed papers are rigorously refereed and the rejection rate is high.

As with the Congress, participation in the open conferences is open to all and papers may be invited or submitted. Again, submitted papers are stringently refereed.

The working conferences are structured differently. They are usually run by a working group and attendance is small and by invitation only. Their purpose is to create an atmosphere conducive to innovation and development. Refereeing is less rigorous and papers are subjected to extensive group discussion.

Publications arising from IFIP events vary. The papers presented at the IFIP World Computer Congress and at open conferences are published as conference proceedings, while the results of the working conferences are often published as collections of selected and edited papers.

Any national society whose primary activity is in information may apply to become a full member of IFIP, although full membership is restricted to one society per country. Full members are entitled to vote at the annual General Assembly, National societies preferring a less committed involvement may apply for associate or corresponding membership. Associate members enjoy the same benefits as full members, but without voting rights. Corresponding members are not represented in IFIP bodies. Affiliated membership is open to non-national societies, and individual and honorary membership schemes are also offered.

# VLSI-SoC: FROM SYSTEMS TO SILICON

Proceedings of IFIP TC 10, WG 10.5, Thirteenth International Conference on Very Large Scale Integration of System on Chip (VLSI-SoC 2005), October 17-19, 2005, Perth, Australia

Edited by

**Ricardo Reis** Universidade Federal do Rio Grande do Sul, Brazil

Adam Osseiran Edith Cowan University, Australia

Hans-Joerg Pfleiderer ULM University, Germany

Edited by R. Reis, A. Osseiran, and H.-J. Pfleiderer

Library of Congress Control Number: 2007930377

#### VLSI-SoC: From Systems to Silicon

p. cm. (IFIP International Federation for Information Processing, a Springer Series in Computer Science)

ISSN: 1571-5736 / 1861-2288 (Internet) ISBN: 13: 978-0-387-73660-0 eISBN: 13: 978-0-387-73661-7

Printed on acid-free paper

Copyright © 2007 by International Federation for Information Processing.

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

987654321

springer.com

# CONTENTS

| Preface                                                                                                                                                                                                                                                                                                     | ix |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Molecular Electronics – Devices and Circuits Technology</b><br>Paul Franzon, David Nackashi, Christian Amsinck, Neil DiSpigna,<br>Sachin Sonkusale                                                                                                                                                       | 1  |

| <b>Improving DPA Resistance of Quasi Delay Insensitive Circuits</b><br><b>Using Randomly Time-shifted Acknowledgement Signals</b><br><i>Fraidy Bouesse, Marc Renaudin, Gilles Sicard</i>                                                                                                                    | 11 |

| A Comparison of Layout Implementations of Pipelined and Non-<br>Pipelined Signed Radix-4 Array Multiplier and Modified Booth<br>Multiplier Architectures<br>Leonardo L. de Oliveira, Cristiano Santos, Daniel Ferrão,<br>Eduardo Costa, José Monteiro, João Baptista Martins, Sergio Bampi,<br>Ricardo Reis | 25 |

| <b>Defragmentation Algorithms for Partially Reconfigurable Hardware</b><br>Markus Koester, Heiko Kalte, Mario Porrmann, Ulrich Rückert                                                                                                                                                                      | 41 |

| <b>Technology Mapping for Area Optimized Quasi Delay Insensitive</b><br><b>Circuits</b><br><i>Bertrand Folco, Vivian Brégier, Laurent Fesquet, Marc Renaudin</i>                                                                                                                                            | 55 |

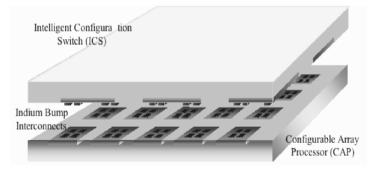

| <b>3D-SoftChip: A Novel 3D Vertically Integrated Adaptive</b><br><b>Computing System</b><br><i>Chul Kim, Alex Rassau, Stefan Lachowicz, Saeid Nooshabadi,</i><br><i>Kamran Eshraghian</i>                                                                                                                   | 71 |

| Caronte: A methodology for the Implementation of Partially                                                                                                       | 87  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| dynamically Self-Reconfiguring Systems on FPGA Platforms                                                                                                         |     |

| Alberto Donato, Fabrizio Ferrandi, Massimo Redaelli,                                                                                                             |     |

| Marco Domenico Santambrogio, Donatella Sciuto                                                                                                                    |     |

| A Methodology for Reliability Enhancement of Nanometer-Scale<br>Digital Systems Based on <i>a-priori</i> Functional Fault-Tolerance<br>Analysis                  | 111 |

| Milos Stanisavljevic, Alexandre Schmid, Yusuf Leblebici                                                                                                          |     |

| Issues in Model Reduction of Power Grids                                                                                                                         | 127 |

| João M. S. Silva, L. Miguel Silveira                                                                                                                             |     |

| A Traffic Injection Methodology with Support for System-Level Synchronization                                                                                    | 145 |

| Shankar Mahadevan, Federico Angiolini, Jens Sparsø,<br>Luca Benini, Jan Madsen                                                                                   |     |

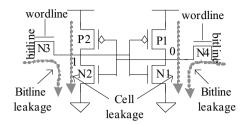

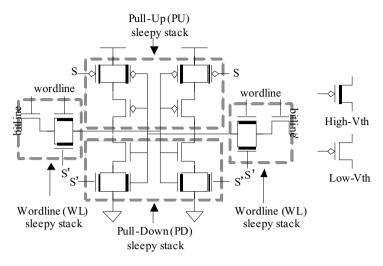

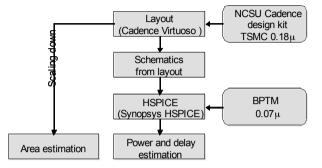

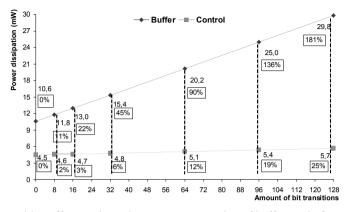

| Pareto Points in SRAM Design Using the Sleepy Stack Approach<br>Jun Cheol Park, Vincent Mooney III                                                               | 163 |

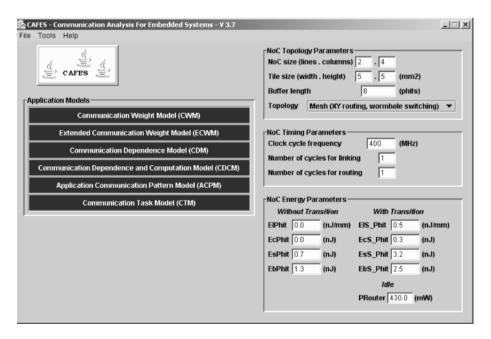

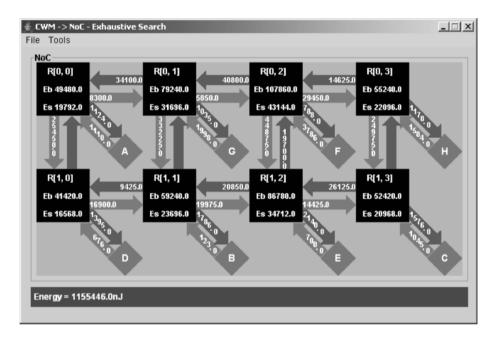

| Modeling the Traffic Effect for the Application Cores Mapping<br>Problem onto NoCs                                                                               | 179 |

| César A. M. Marcon, José C. S. Palma, Ney L. V. Calazans,<br>Fernando G. Moraes, Altamiro A. Susin, Ricardo A. L. Reis                                           |     |

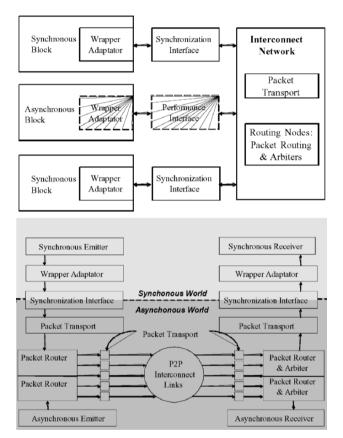

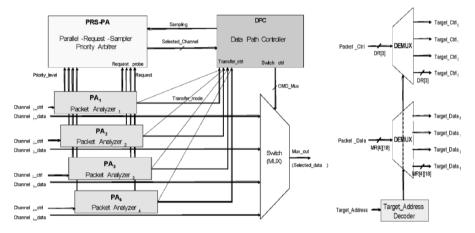

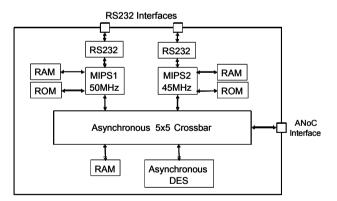

| Modular Asynchronous Network-on-Chip: Application to GALS<br>Systems Rapid Prototyping<br>Jérôme Quartana, Laurent Fesquet, Marc Renaudin                        | 195 |

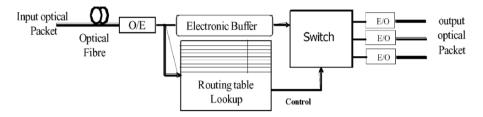

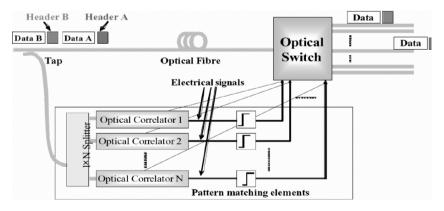

| A Novel MicroPhotonic Structure for Optical Header Recognition<br>Muhsen Aljada, Kamal Alameh, Adam Osseiran, Khalid Al-Begain                                   | 209 |

| <b>Combined Test Data Selection and Scheduling for Test Quality</b><br><b>Optimization under ATE Memory Depth Constraint</b><br><i>Erik Larsson, Stina Edbom</i> | 221 |

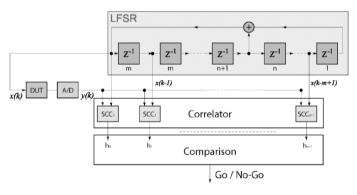

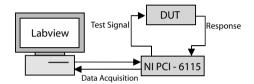

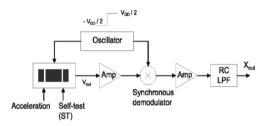

| <b>On-chip Pseudorandom Testing for Linear and Nonlinear MEMS</b><br>Achraf Dhayni, Salvador Mir, Libor Rufer, Ahcène. Bounceur                                  | 245 |

| Scan Cell Reordering for Peak Power Reduction during<br>Scan Test Cycles<br>N. Badereddine, P. Girard, S. Pravossoudovitch, A. Virazel,<br>C. Landrault                                                     | 267 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>On The Design of A Dynamically Reconfigurable Function-Unit</b><br><b>for Error Detection and Correction</b><br><i>Thilo Pionteck, Thomas Stiefmeier, Thorsten Stoake,</i><br><i>Manfred Glesner</i>     | 283 |

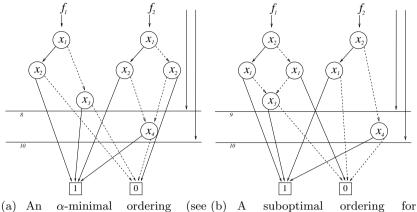

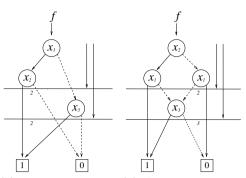

| <b>Exact BDD Minimization for Path-Related Objective Functions</b><br><i>Rüdiger Ebendt, Rolf Drechsler</i>                                                                                                 | 299 |

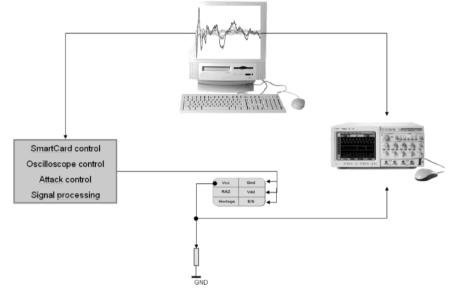

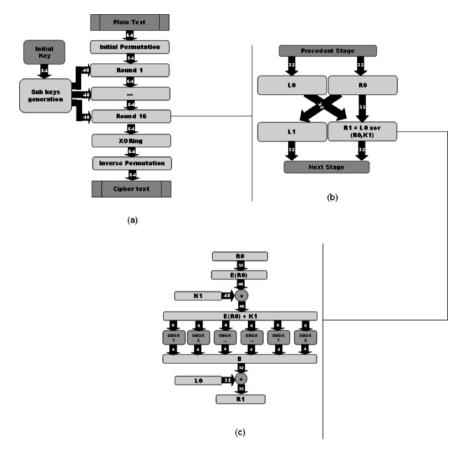

| <b>Current Mask Generation: an Analog Circuit to Thwart DPA</b><br><b>Attacks</b><br>Daniel Mesquita, Jean-Denis Techer, Lionel Torres, Michel<br>Robert, Guy Cathehras, Gilles Sassatelli, Fernando Moraes | 317 |

| A Transistor Placement Technique Using Genetic Algorithm and<br>Analytical Programming                                                                                                                      | 331 |

Cristiano Lazzari, Lorena Anghel, Ricardo A. L. Reis

# PREFACE

This book contains extended and revised versions of the best papers that were presented during the thirteenth edition of the IFIP TC10/WG10.5 International Conference on Very Large Scale Integration, a Global System-on-a-Chip Design & CAD conference. The 13th conference was held at the Parmelia Hilton Hotel, Perth, Western Australia (October 17-19, 2005). Previous conferences have taken place in Edinburgh, Trondheim, Vancouver, Munich, Grenoble, Tokyo, Gramado, Lisbon, Montpellier and Darmstadt.

The purpose of this conference, sponsored by IFIP TC 10 Working Group 10.5, is to provide a forum to exchange ideas and show industrial and academic research results in the field of microelectronics design. The current trend toward increasing chip integration and technology process advancements brings about stimulating new challenges both at the physical and system-design levels, as well in the test of these systems. VLSI-SOC conferences aim to address these exciting new issues.

The 2005 edition of VLSI-SoC maintained the traditional structure, which has been successful at the previous VLSI-SOC conferences. The quality of submissions (107 papers from 26 countries) made the selection process difficult, but finally 63 papers and 25 posters were accepted for presentation in VLSI-SoC 2005. Out of the 63 full papers presented at the conference, 20 were chosen by a selection committee to have an extended and revised version included in this book. These selected papers came from Australia, Brazil, France, Germany, Italy, Korea, Portugal, Sweden, Switzerland, United Kingdom and the United States of America.

Furthermore, this book includes an excellent paper entitled "Molecular Electronics – Devices and Circuits Technology" presented at the conference, as an invited talk, by Professor Paul Franzon from North Carolina State University.

VLSI-SoC 2005 was the culmination of many dedicated volunteers: paper authors, reviewers, session chairs, invited speakers and various committee chairs, especially the local arrangements organizers. We thank them all for their contribution.

This book is intended for the VLSI community mainly to whom that did not have the chance to take part in the VLSI-SOC 2005 Conference. The papers were selected to cover a wide variety of excellence in VLSI technology and the advanced research they describe. We hope you will enjoy reading this book and find it useful in your professional life and to the development of the VLSI community as a whole.

The editors

April 2007

# Molecular Electronics – Devices and Circuits Technology

Paul Franzon, David Nackashi, Christian Amsinck, Neil DiSpigna, Sachin Sonkusale Department of Electrical and Computer Engineering North Carolina State University, Raleigh, NC, USA paulf@ncsu.edu

**Abstract.** Molecular electronics holds significant potential to outscale bulk electronic devices. However, practical issues have limited that potential to date. This paper reviews the function and design of molecular electronics and evaluates results to date in a circuits context.

# 1. Introduction

Molecular electronics has several potential advantages for being of interest as an electronic element. It has small size, typically on the range of a few nm, well below the total size projected for any FET. A second advantage is that molecules can self assemble onto surfaces, a very low-cost process. Their third advantage is that they can be designed at the atomic level, a feat not possible with bulk devices. Atomic level design permits a wide range of devices to be investigated, and potentially leads to precise control of electronic properties. For example, switching between isomers of the same chemistry should lead to radically different device properties.

This paper presents a two-level overview of molecular electronics. Section 2 focuses on device physics and understanding, while Section 3 evaluates some of these devices within a circuit's context.

# 2. Molecular Devices

Since the first suggestion that molecular elements could be designed to control electronic properties in a circuit [1], the vast majority of research in molecular electronics has focused on measuring and predicting electronic transport through organic devices. Organic materials of all types have been studied, including metallic and semiconducting carbon nanotubes, silicon nanowires, oligo(phenylene ethnylene) (OPE) based bistable molecular switches, insulating alkanethiol chains,

slightly more conductive OPEs and oligo(phenylene vinylene)s (OPVs), and chargestorage molecular systems such as ferrocenes. Understanding electron transport and charge storage is extremely important to advance the process of engineering molecules for specific applications.

Where silicon device characteristics are engineered by varying the carrier density through doping techniques, designing molecular devices involves modifying electronic wavefunctions at a metal-molecule-metal junction [2] However, as silicon devices continue to shrink, the current modeling techniques become less accurate as the channel lengths no longer exhibit bulk properties [3]. This has resulted in a great deal of harmony between the fields of silicon nanoelectronics and molecular electronics, with each group leveraging off the knowledge created by the other.

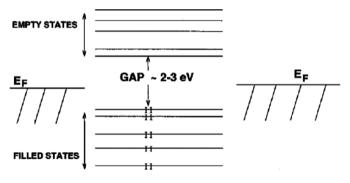

Most of the molecular electronic compounds listed above are only just a few angstroms to tens of angstroms in length. With only a few atoms involved in electron transfer, the notion of a density of states becomes less accurate and the properties of these molecules are better described by the location and energy gaps of their highest occupied molecular orbital (HOMO) and lowest unoccupied molecular orbital (LUMO). With a few exceptions such as metallic and semiconducting carbon nanotubes, it is expected that the Fermi levels of the metallic contacts will lie within the HOMO-LUMO gap of most molecules. This is illustrated in Figure 1, where the energy gap within most molecules is likely to be approximately 2-3 eV.

Fig. 1. Metal-Molecule-Metal junction. From Samanta et al. [4], "Electronic conduction through organic molecules."

With this model, it is expected that the primary mode of electron transfer will be tunneling, rather than propagation. A simple approximation for tunneling current through a molecular junction can be modeled using the expression,  $k_{ET} = k_0 e^{-\beta d}$ , where  $k_{ET}$  is the rate of electron transfer, d is the barrier width (length of the molecule), and  $\beta$  is a constant defined by the electronic structure of the organic layer. This approximation simply states that for set of similar molecules varying in length (such as alkanethiols with varying numbers of methylene groups), the current density (at a given voltage) across the junction will exponentially decrease as the molecular length increases. This is seen quite clearly in alkane chain conductivity research using mercury drop electrodes, nanopores and STM analysis. However comparing

two structurally different molecules whose lengths are the same, research has shown that the tunneling currents can be very different. This has lead to the belief that the parameter  $\beta$  can be used to describe the electron transmission properties of different molecules.

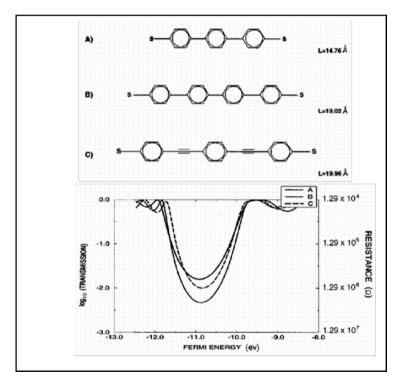

Experimental research has shown that molecules exhibiting a highly  $\pi$ conjugated structure (such as OPEs and OPVs), as compared to the  $\sigma$ -bonded alkane chains, have a much lower gap resistance in metal-molecule-metal structures. This suggests that the barrier to electron transfer is lowered within molecules containing delocalized electron clouds. To more accurately account for scattering (which is neglected in the tunneling approximation) and the specific electronic structure for various molecules, many theorists use Density Functional and Green's Function based approaches for more accurate evaluations. An example of the value in these approaches is shown in Figure 2, where the transmission properties for three different molecules were calculated and plotted. Samanta and Datta [4] found that the resistance of a four benzene chain molecule scaled higher as expected when compared to a shorter, three benzene molecule. However, a three ring OPE was found to have a lower resistance than the four ring benzene chain, even though the OPE is a longer molecule. This was attributed to the presence of the triple bond in the OPE, causing a more delocalized electronic structure.

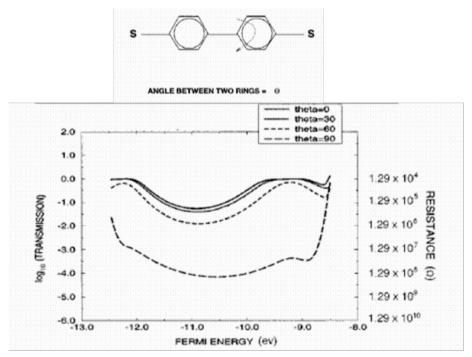

In the same study, Samanta calculated the transmission properties of a two ring benzene chain as a function of the ring orientation to each other. Shown in Figure 3, the most conductive state is when the molecule has no offset, or

Fig. 2. Green-function analysis of electronic transmission through different molecules. From Samanta, et al. [4], "Electronic conduction through organic molecules."

is planar, and the least conductive state is when the rings are 90° out of phase. This theoretical work further suggests that delocalized, overlapping p orbitals play an import part in lowering the barrier for electronic conduction. Experimentally, this was also shown in two separate test structures comparing OPE and OPV molecules. OPV molecules, known to be more planar and exhibiting less bond-length alternation, were determined to have a slightly lower gap resistance.

Many have suggested using a third gate electrode to modulate transmission properties through a molecule by twisting or bending the molecular backbone, however concentrating a strong enough field in a gap less than 50 angstroms is extremely difficult. A theoretical study of a molecular three terminal device was performed by Datta<sup>i</sup> at Purdue, using a single benzene ring as the conductive channel. To get good control of the channel, i.e., to get a high enough field to modulate the device, the equivalent gate oxide would need to be less than 10% of the channel length. This suggests that the gate electrode would need to be within two angstroms of the benzene ring, placed within an atomic level of accuracy. For these reasons, most research into molecular electronics has focused on two terminal devices, primarily switches.

**Fig. 3.** Ring orientation effects on the transmission property. From Samanta, et al. [4], "Electronic conduction through organic molecules."

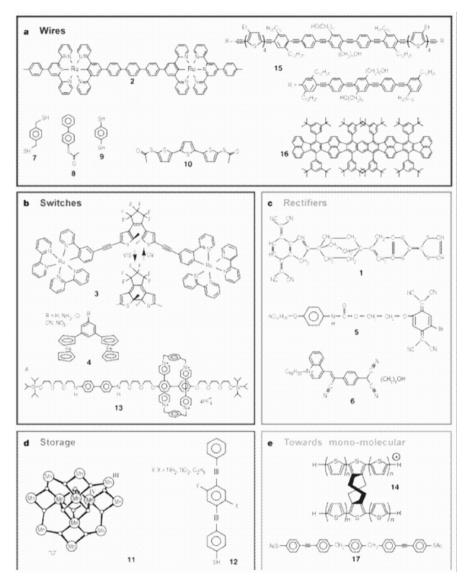

The growing body of theoretical work and tools used to generate molecular models has lead to many suggestions for novel, molecular devices. Shown in Figure 4 are several examples of these devices, which include switches, wires, rectifiers and storage devices. Of course, the only way to determine the validity of theoretical models used to generate these suggestions is through experimental analysis, an area just now developing on its own. The contact to the molecule itself, atomic in nature, is just as much a part of the device as the organic structure itself. Although theoretical studies have helped to understand the nature of the metal-molecular contact, finding a consistent, scalable and repeatable test bed for comparing different molecules has proven to be the most challenging aspect of molecular characterization.

# 3. Circuits and Scaling for Molecular Electronics

It can be argued that to be a true successor technology to CMOS, molecular electronics needs to provide two of more generations of scaling beyond the silicon 18 nm node. That is provide continued scaling in some or more metrics of fundamental performance in computing, particularly computation throughput, power per operation, and cost per unit throughput; while achieving similar system availability and reliability rates to those achieved today.

These are challenging metrics to evaluate especially for an immature technology. This section will start off by reviewing the basics behind molecular electronics, and provide a summary evaluation of the potential, and roadblocks, for molecular electronics to provide continued scaling beyond the end of CMOS, in these metrics.

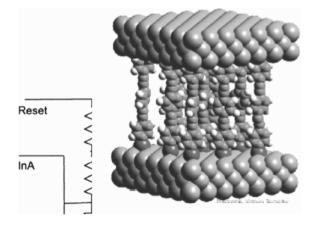

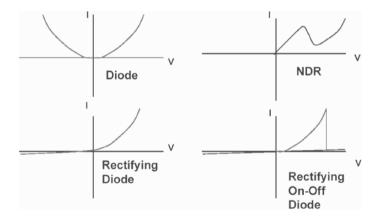

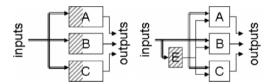

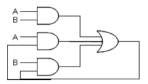

For reasons discussed above, all practical proposed and demonstrated molecular electronic devices are two terminal devices. For example, the illustration in Figure 5 is that of an atomic level presentation of benzene thiol molecules assembled between two gold contacts. The density potential of this technology is evident when it is realized that the molecule illustrated in Figure 5 is only 3.2 nm long. Generally speaking the principle of operation behind these devices is that a change in the longitudinal electric field causes a temporary or permanent change in the electron cloud configuration around the molecule and thus its conductivity. The molecule thus behaves like a tunneling diode. Measured results have shown characteristics that include non-rectifying diodes, rectifying diodes (by using different metals in the two contacts), diodes displaying negative differential resistance (NDR) and two-state (on-off) diodes, with an on-state and an off-state (Figure 6) [1]. Note that in Figure 6 only the rectifying version of the two-state diode is shown, as it is much more useful than the non-rectifying version. Of these characteristics devices, only the NDR and the rectifying on-off diodes are useful for logic, and even then present challenges over their 3-terminal predecessors.

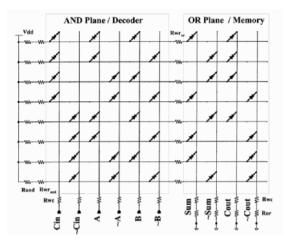

In order to evaluate the potential of these devices, NAND gate configurations were compared with that of a ~2018 18 nm node CMOS NAND gate. Figure 7 shows a possible circuit topology that uses the NDR diode to make a NAND gate and a circuit topology to build a programmable logic array using rectifying on-off diodes (only the on diodes are shown). Though the NDR-based circuit is impractical, it is included for completeness. The PLA structure requires a gain element to be practical. It is assumed that it is rebuffered using CMOS gates.

**Fig. 4.** Suggested molecular electronic devices. From Joachim et al. [6] "Electronics using hybrid-molecular and mono-molecular devices."

These three circuit topologies are evaluated against some useful performancerelated metrics in Table 1. The values for the 18 nm node NAND gate are taken from, or calculated using, data in the International Technology Roadmap for Semiconductors. The values for the molecular circuits are calculated using simple techniques and are likely to be wrong by several orders of magnitude. The area estimate for the PLA is made assuming an 8 nm wire imprint technology and (very pessimistically) and 2x area overhead for the peripheral circuits. The molecular device is assumed to have an on current of 500 nA and an off current of 50 nA. The delay and power estimates are made from circuit level calculations, not from the underlying physics.

Fig. 5. Benzene Thiol molecules between two gold contacts. (Courtesy, Seminario).

Fig. 6. Generic IV characteristics for molecular diodes.

Fig. 7. Examples of circuits built using NDR (left side) and rectifying on-off diodes (right side). Source[7].

| Circuit                                            | Area           | Energy<br>per 010<br>transition | Leakage<br>Power      | Delay  |

|----------------------------------------------------|----------------|---------------------------------|-----------------------|--------|

| 18 nm 2-input                                      | 0.2            | $10^{-17} J$                    | $10^{-7} \mathrm{W}$  | 5 ps   |

| NAND gate                                          | sq.µm          |                                 |                       |        |

| NDR gate                                           | 0.1<br>sq.µm?  | 10 <sup>-16</sup> J             | 10 <sup>-12</sup> W   | 1 µs   |

| 2-input NAND<br>equivalent<br>within larger<br>PLA | 0.01<br>sq.µm. | 10 <sup>-16</sup> J             | $10^{-7}  \mathrm{W}$ | 100 ps |

Table 1. Area and Performance Estimates for CMOS and molecular nanotechnologies.

Unsurprisingly, given the use of two-terminal devices, the only aspect in which molecular electronics outperforms 18 nm CMOS is area. Delay is significantly worse, and power comparable. The energy\*delay product is worst in the molecular case, while the area\*delay product is comparable.

This analysis leads to the tentative conclusion that most likely the best application for molecular electronics is in large relatively slow memories, and devices that benefit from such memories. Then the key question is what is the real density likely to be achieved by a molecular memory. There are two sub questions here – what is the peak density and what is the achievable density when peripheral circuits are accounted for?

The peak density is related to the smallest wire that can be imprinted – likely to be around 5 nm wide. This gives a unit cell size of 10x10 nm, or a device density of 10,000 devices per sq.µm., equivalent to a peak density of  $10^{12}$  devices per sq.cm., or more than 10 full length DVD movies on a chip!

However, the achievable density is limited by the overhead required for address decoders, sense-amps, etc. This, in turn, is limited by the largest subarray that can be built and read with sufficiently low error rate. This has been analyzed and the results presented in Table 2. The achievable sub-array size depends solely on the on:off ratio achieved by the diode. For reference, measured data seems to indicate on:off ratios today of around 10:1 for truly molecular devices. In contrast today's DRAMs are built using 10,000 x 10,000 subarrays. It is clear that larger on:off ratios are needed to achieve reasonable overheads. Fortunately, a number of nano-engineered device concepts are under investigation that has potential to achieve the required on:off ratio.

**Table 2.** The maximum sub-array size that can be built for different molecular diode on:off ratios.

| On:off Ratio | Max. Array |

|--------------|------------|

| 7:1          | 64x64      |

| 13:1         | 128x128    |

| 100:1        | 1225x1225  |

| 1000:1       | 12kx12k    |

| 8000:1       | 1Mx1M      |

# 4. Conclusions

While molecular electronics holds significant potential, achieving that potential in a technologically useful fashion is very challenging. Challenges include the following. First there is the difficulty of integrating molecules with bulk materials in ways that the limitations of the latter do not dominate the device operation. This is why filament switching dominates many of the collected results. Second is achieving the challenge of achieving sufficient device performance such that molecules can outscale silicon in a metric beside size. However, with increased understanding of molecular design and performance, together with improving abilities to fabricate nano-ordered materials, molecular electronics is still a promising future technology.

# References

- 1. A. Aviram, M.A. Ratner, "Molecular rectifiers," Chem Phys. Lett., 29, 277, 1974.

- 2. C. Joachim, J.K. Gimzewski, A. Aviram, "Electronics using hybrid-molecular and mono-molecular devices," Nature, **408**, 541-548, 2000.

- 3. Robert W. Keyes, "Fundamental Limits of Silicon Technology," Proc. IEEE, **89**, 227-239, 2001.

- 4. M.P. Samanta, W. Tian, S. Datta, J.I. Henderson, C.P. Kubiak, "Electronic conduction through organic molecules," Phys. Rev. B, **53**, 7626-7629, 1999.

- Prashant Damle, Titash Rakshit, Magnus Paulsson, Supriyo Datta, "Current-Voltage Characteristics of Molecular Conductors: Two Versus Three Terminal," IEEE Nano, 1, 145-153, 2002.

- 6. C. Joachim, J.K. Gimzewski, A. Aviram, "Electronics using hybrid-molecular and mono-molecular devices," Nature, **408**, 541-548, 2000.

- M.R. Stan, P.D. Franzon, S.C. Goldstein, J.C. Lach, M. Zigler, "Molecular Electronics: from devices and interconnect to circuits and architecture," Proc. IEEE, 91(11), Nov. 2003, pp. 194-1957.

# Improving DPA Resistance of Quasi Delay Insensitive Circuits Using Randomly Timeshifted Acknowledgment Signals

F. Bouesse, M. Renaudin, G. Sicard TIMA Laboratory, Concurent Integrated Systems Group 26 av. Félix Viallet, 38031 Grenoble Cedex fraidy.bouesse@imag.fr

**Abstract.** The purpose of this paper is to propose a design technique for improving the resistance of the Quasi Delay Insensitive (QDI) Asynchronous logic against Differential Power Analysis Attacks. This countermeasure exploits the properties of the QDI circuit acknowledgement signals to introduce temporal variations so as to randomly desynchronize the data processing times. The efficiency of the countermeasure, in terms of DPA resistance, is formally presented and analyzed. Electrical simulations performed on a DES crypto-processor confirm the relevancy of the approach, showing a drastic reduction of the DPA peaks, thus increasing the complexity of a DPA attack on QDI asynchronous circuits.

# 1 Introduction and motivations

Nowadays, the possibilities offered by all recent powerful side-channel attacks to access to confidential information, constrain secure systems providers to develop new resistant systems against these attacks. Among these new hardware cryptanalysis attacks, there is the Differential Power Analysis (DPA) which is one of the most powerful and low cost attack. The main idea behind DPA is that there exists a correlation between data processed by the design and the observable power consumption. In 1998 Paul Kocher [1] demonstrated how this correlation can be exploited using statistical means to retrace secret key information.

It is in this context that the properties of Self-timed logic have been exploited in order to propose efficient counter-measures against DPA attacks [2][3].

All results from the analysis of Self-timed logic particularly the Quasi Delay Insensitive asynchronous logic demonstrated the potentiality of this type of logic to increase the chip's resistance [4][5].

However, paper [6] reported that, even if the QDI asynchronous logic increases the resistance of the chip, there still exists some residual sources of leakage that can be used to succeed the attack.

The objective of this paper is to make a DPA attack impossible or impracticable with standard equipment by increasing the complexity of the attack. For doing so, we introduce randomly time shifted (RTS) acknowledgment signals in the QDI asynchronous logic in order to add noise in chip's power consumption. Indeed, the use of a RTS acknowledgement signal in an asynchronous Quasi Delay Insensitive block enables us to desynchronize the data processing time, so as to compute the blocks' output channels at random times. As the DPA attack requires the signals to be synchronized with respect to a fixed time instant for data analysis [1][7], this desynchronization makes the DPA attack more difficult as it is proved in this paper.

We present in the first part of the paper (section 2), the properties of Quasi Delay Insensitive asynchronous logic, especially the properties of the acknowledgment signal. Section 3 first introduces the formal analysis of the DPA attack. It then presents the desynchronization technique based on RTS acknowledgement signals and formalizes its efficiency in terms of DPA resistance. Finally, sections 4 and 5 illustrate the technique using electrical simulations performed on the well known Data Encryption Standard (DES) architecture. Section 6 concludes the paper and gives some prospects.

# 2 Quasi Delay Insensitive Asynchronous logic: the acknowledgment signal

This section recalls the basic characteristics of an asynchronous circuit, particularly the rule of the acknowledgement signal in the QDI asynchronous logic.

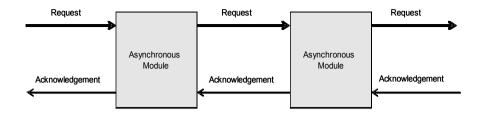

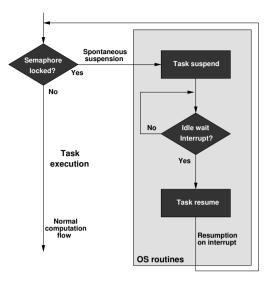

Because this type of circuit does not have a global signal which samples the data at the same time, asynchronous circuits require a special protocol to perform a communication between its modules. The behavior of an asynchronous circuit is similar to a data-flow model. The asynchronous module, as described in figure 1 and which can actually be of any complexity, receives data from its input channels (request signal), processes them, and then sends the results through its output channels. Therefore, a module is activated when it senses the presence of incoming data. This point-to-point communication is realized with a protocol implemented in the module itself. Such protocols necessitate a bi-directional signaling between both modules (request and acknowledgement): it is called handshaking protocols.

Fig. 1. Handshake based communication between modules.

The basis of the sequencing rules of asynchronous circuits lies in the handshaking protocols. Among the two mains classes of protocols, only the four-phase protocol is considered and described in this work. It is the most widely used and efficiently implemented in CMOS [8].

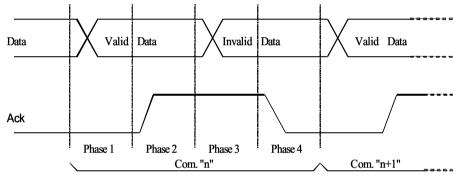

Fig. 2. Four-phase handshaking protocol.

In the first phase (Phase 1) data are detected by the receiver when their values change from invalid to valid states. Then follows the second phase where the receiver sets to one the acknowledgement signal. The sender invalidates all data in the third phase. Finally the receiver resets the acknowledgment signal which completes the return to zero phase.

Dedicated logic and special encoding are necessary for sensing data validity/invalidity and for generating the acknowledgement signal. Request for computation corresponds to data detection and the reset of the acknowledgment signal means that the computation is completed and the communication is finished.

In QDI asynchronous logic, if one bit has to be transferred through a channel with a four-phase protocol, two wires are needed to encode its different values. This is called dual-rail encoding (table 1).

| Channel data | A0 | A1 |

|--------------|----|----|

| 0            | 1  | 0  |

| 1            | 0  | 1  |

| Invalid      | 0  | 0  |

| Unused       | 1  | 1  |

Table 1. Dual rail encoding of the three states required to communicate 1 bit.

This encoding can be extended to N-rail (1-to-N).

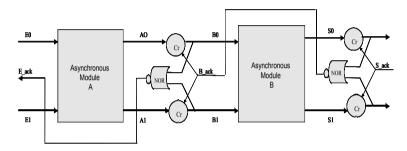

The acknowledgement signal is generated using the data-encoding. The dual-rail encoded outputs are sensed with Nor gates for generating the acknowledgment signal, as illustrated in figure 3.

**Fig. 3.** 1-bit Half-buffer implementing a four-phase protocol (Cr is a Muller gate with a reset signal)

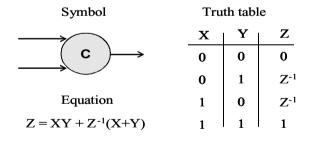

The Muller C-element's truth table and symbol are given in Figure 4.

Fig. 4. Truth table and symbol of the C-element.

Figure 3 illustrates the implementation of two asynchronous modules (A and B) with their memory elements called half-buffer. The half-buffer implements a fourphase protocol. When the acknowledgement signal of module B ( $B\_ack$ ) is set, it means that the module is ready to receive data. If a data is transferred from module A to module B, module B computes its outputs and resets its acknowledgement signal ( $B\_ack$ ). Module B is then ready to receive invalid data from module A.

In this operating mode, the acknowledgment signal can be considered as a local enable signal which controls data storage locally. Note that this mechanism does not need any timing assumption to ensure functional correctness; it is simply sensitive to events. Hence, the acknowledgment signal enables to control the activation of the computation in a given module, as well as its time instant.

The technique proposed in this paper, exploits this property by inserting random delays in the acknowledgement signals. It is called Randomly Time-Shifted acknowledgment signals. It basically desynchronizes the power consumption curves making the differential power analysis more difficult as proved in the next section.

# **3** DPA and RTS acknowledgment signal on QDI asynchronous circuits: Formal Approach

In this section, we formally introduce the basis of the DPA attack [7] and formally analyse the effects of the RTS acknowledgement signal on QDI asynchronous circuits in terms of DPA resistance.

#### 3.1 Differential Power Analysis Attack

The functional hypothesis of DPA attack is the existing correlation between the data processed by the circuitry and its power consumption. There are three main phases for processing the DPA attack: the choice of the selection function D, the data collection phase and the data analysis phase.

**Phase 1**: In the first step, the selection function is defined by finding blocks in the architecture which depend on some parts of the key. Such a function in the DES algorithm for example can be defined as follows:

$D(C_{l_{b}}P_{\phi}K_{\theta}) = SBOX1(P_{\phi} \bigoplus K_{\theta})$   $C_{1} = first \ bit \ of \ SBOX1 \ function.$   $P_{6} = 6 \text{-bit plain-text-input of the } SBOX1 \ function.$   $K_{\theta} = 6 \text{-bit of the first round's subkey: key to guess.}$   $SBOX1 = a \ substitution \ function \ of \ DES \ with \ a \ 4 \text{-bit output.}$

**Phase 2**: The second step consists in collecting the discrete time power signal  $S_i(t_j)$  and the corresponding ciphertext outputs  $(CTO_i)$  for each of the N plaintext inputs  $(PTI_i)$ . The power signal  $S_i(t_j)$  represents the power consumption of the selection function: index *i* corresponds to the  $PTI_i$  plaintext stimulus and time  $t_j$  corresponds to the time where the analysis takes place.

**Phase 3**: The right key is guessed in the third phase. All current signals  $S_i(t_j)$  are split into two sets according to a selection function *D*.

$$S_{0} = \left\{ S_{i}(t_{j}) | D = 0 \right\}$$

$$S_{1} = \left\{ S_{i}(t_{j}) | D = 1 \right\}$$

<sup>(1)</sup>

The average power signal of each set is given by:

$$A_{0}(t_{j}) = \frac{1}{|n_{0}|} \sum_{i=1}^{n_{0}} S_{i}(t_{j})$$

$$A_{1}(t_{j}) = \frac{1}{|n_{1}|} \sum_{i=1}^{n_{1}} S_{i}(t_{j})$$

(2)

Where  $|n_o|$  and  $|n_I|$  represent the number of power signals  $S_i(t_j)$  respectively in set  $S_0$  and  $S_1$ . The DPA bias signal is obtained by:

$$S(t_{i}) = A_{0}(t_{i}) - A_{1}(t_{i})$$

(3)

If the DPA bias signal shows important peaks, it means that there is a strong correlation between the D function and the power signal, and so the guessed key is correct. If not, the guessed key is incorrect.

Selecting an appropriate D function is then essential in order to guess a good secret key.

As illustrated above, the selection function D computes at time  $t_j$  during the ciphering (or deciphering) process, the value of the attacked bit. When this value is manipulated at time  $t_j$ , there will be at this time, a difference on the amount of dissipated power according to the bit's value (either one or zero).

Let's define  $d_{0i}(t_j)$  the amount of dissipated power when the attacked bit switches to 0 at time  $t_j$  by processing the plaintext input *i* and define  $d_{1i}(t_j)$  the amount of dissipated power when this bit switches to 1.

In reality, the values of  $d_{0i}(t_j)$  and  $d_{1i}(t_j)$  correspond to the dissipated power of all data-paths which contribute to the switching activity of the attacked bit. Each one of these values has its weight in each average power signal  $A_0(t_j)$  and  $A_1(t_j)$ . As the goal of the DPA attack is to compute the difference between these two values, we can express the average power signal of these both sets  $A_0(t_j)$  and  $A_1(t_j)$  by:

$$A_{0}(t_{j}) = \varepsilon_{0}(t_{j}) = \frac{1}{|n_{0}|} \sum_{i=1}^{n_{0}} d_{0i}(t_{j})$$

$$A_{1}(t_{j}) = \varepsilon_{1}(t_{j}) = \frac{1}{|n_{1}|} \sum_{i=1}^{n_{1}} d_{1i}(t_{j})$$

(4)

Therefore, the DPA signature is expressed by:

$$\varepsilon_0(t_i) - \varepsilon_1(t_i) = \varepsilon(t_i) \tag{5}$$

In order to make an efficient analysis, the amplitude of the DPA signature  $\varepsilon(t_j)$  must be as high as possible.

A simple way to guarantee this is to use a significant number of plaintext inputs (*N*). Indeed, the number of *PTIi* (the number of power signal  $S_i(t_j)$ ) used to implement the attack enables to reduce the effects of the noisy signals and to increase the probability of exciting all data-paths.

• It is well known that the signal-to-noise ratio for the averaged signal increases as the square root of the number of curves.

$$SNR = \sqrt{N} \frac{S_{signal}}{\sigma_{noise}}$$

$\sigma_{noise}$  is the standard deviation of the noise

• Increasing the number of plaintext inputs (PTIi) allows us to ensure that all data-paths which make switching to 0 or to 1 the attacked bit are excited. The deal here, is to take into consideration all possible quantities dxi(tj) which represent the switching current of the attacked bit. As the probability of exciting all data-paths is proportional to N, bigger the value of N, better the probability to excite all data-paths of the attacked bit is:

$$P(\omega) = \frac{N}{m}$$

m is generally unknown by the hacker and represents the number of datapaths.

Therefore, the knowledge of the implementation which enables to choose the plaintext inputs and the use of high quality instrumentation are assets that improve the DPA attack. In fact, they considerably reduce the number of data (N) required for succeeding the attack.

#### 3.2 The RTS acknowledgement signal

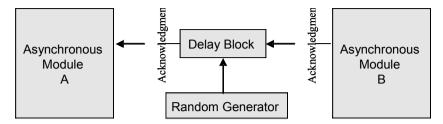

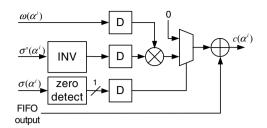

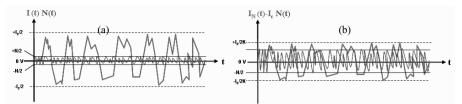

The method we propose in this paper enables the designer to introduce a temporal noise in the design in order to desynchronize the time required for processing the attacked bit. The idea of the approach is to randomly shift in time the current profile of the design. To achieve this goal, we randomize the acknowledgment signal latency of the blocks of the architecture. As illustrated in figure 5, we use a delay element controlled by a random number generator. The design of the random number generator is out of the scope of this paper. True

random number generator (TRNG) design is an important topic and many different types of TRNG implementation exist [9][10].

Fig. 5. Implementation of a random acknowledgment signal

Let's denote *n* the number of possible random delays implemented in a given architecture. *n* depends on the number of available acknowledgment signals (*m*) in the architecture and on the number of delays ( $k_i$ ) implemented per acknowledgment signal. The "*n*" value is computed by the following expression:

$$n = \prod_{i=1}^{m} k_i$$

assuming cascaded modules.

If the acknowledgment signal is randomized *n* times, it means that the value of the attacked bit is computed at *n* different times  $(t_j)$ . *N/n* represents the number of times the attacked bit is processed at a given time  $t_j$  and *N/2n* represents the number of times the quantities  $d_{0i}(t_j)$  and  $d_{1i}(t_j)$  of this bit contribute to set  $S_0$  and  $S_1$  respectively. If we consider that the *N* curves are equally split in both sets  $(n_0=n_1=N/2)$ , the average power signal of each set is now expressed by:

$$\varepsilon_{0}(t) = \frac{1}{n_{0}} \sum_{i=1}^{N/2n} \left( \sum_{j=1}^{n} d_{0i}(t_{j}) \right)$$

$$\varepsilon_{1}(t) = \frac{1}{n_{1}} \sum_{i=1}^{N/2n} \left( \sum_{j=1}^{n} d_{1i}(t_{j}) \right)$$

(6)

The DPA bias signal is then given by the following expression:

$$\varepsilon(t) = \left(\varepsilon_0(t_1) - \varepsilon_1(t_1)\right) + \dots + \left(\varepsilon_0(t_n) - \varepsilon_1(t_n)\right)$$

with

$$\varepsilon_0(t_n) = \frac{1}{n_0} \sum_{i=1}^{N/2n} d_{0i}(t_n) ;$$

Improving DPA resistance of Quasi Delay Insensitive Circuits

$$\varepsilon_1(t_n) = \frac{1}{n_1} \sum_{i=1}^{N/2n} d_{1i}(t_n)$$

(7)

These expressions show that, instead of having a single quantity  $\varepsilon_x(t_j)$ , we have *n* different significant quantities  $\varepsilon_x(t_n)$  which correspond to *n* times where the attacked bit is processed. Moreover, it also demonstrates that each quantity  $\varepsilon_x(t_j)$  is divided by a factor *n* as illustrated by the following simplification:

$$\varepsilon_{x}(t_{j}) = \frac{1}{n_{x}} \left( d_{xj}(t_{j}) + \dots + d_{xn}(t_{j}) \right) \cong \frac{d_{xj}(t_{j})}{n}$$

with

$$d_{xj}(t_{j}) \cong \dots \cong d_{xn}(t_{j})$$

(8)

It means that, although the number of significant points is increased by n, this approach divides by n the average current peaks variations. It offers the possibility to bring down the level of DPA bias signal closer to circuitry's noise.

#### 3.2 Discussion

Let's for example implement the DPA attack using 1000 plaintext inputs (N=1000). In the standard approach where the attacked bit is processed at a unique given time, we obtain an average of 500 current curves for each of the sets  $S_0$  and  $S_1$ .

Using our approach with RTS acknowledgment signals and assuming n=16 (for example), we obtain 16 different points (in terms of time) where the attacked bit is processed. There are 62 values  $d_{xi}(t_j)$  (*N*/*n* curves) where this bit is processed at time  $(t_j)$ . Each set then contains 31 curves. When the average power signal of each set is calculated, values  $d_{xi}(t_j)$  are 16 times lower than without RTS acknowledgment signals. Hence, the contribution of  $d_{xi}(t_j)$  in current peaks variations are reduced by a factor 16.

Therefore, to succeed the attack the hacker is obliged to significantly increase the number of acquisitions (N) or to apply a cross-correlation function which is exactly the goal to achieve in terms of attack's complexity. In fact, cross-correlation remains a useful method for synchronizing data. But to be functional, the hacker must identify the amount of current profile of the attacked bit  $(d_{xi}(t_j))$  to be used as a reference, and then compute cross-correlations in order to synchronize each of the N curves with the reference. Knowing that, the cross-correlation is applied on instantaneous current curves which contain significant quantity of noise.

To increase the difficulty of this analysis, the value of n can be significantly increased by dealing with the values of m and k.

• The value of *m* depends on the architecture. Its value can be increased by expanding the acknowledgment signals of the architecture. Each bit or intermediate value of the design can be separately acknowledged. This technique enables also to reduce the data-path latency.

• The values of the delay depend on the time specification to cipher/decipher data. They are bounded by the maximum ciphering/deciphering time.

Consequently, the acknowledgement signals of any asynchronous quasi delay insensitive circuit can be exploited to introduce random delays and therefore increase the DPA resistance of the chips.

## 4 Case Study: DES Crypto-processor

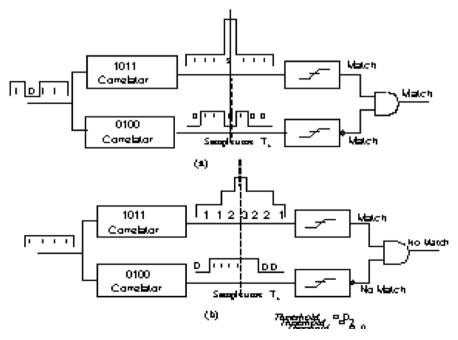

This section deals with the different possibilities of implementing RTS acknowledgment signals on QDI asynchronous circuits. The DES was chosen as an evaluation vector because the attack on this algorithm is well known.

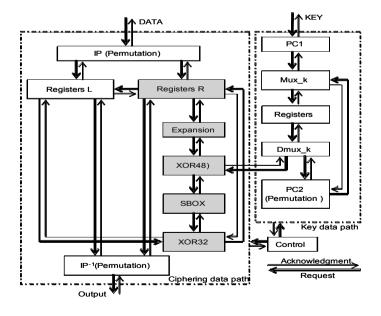

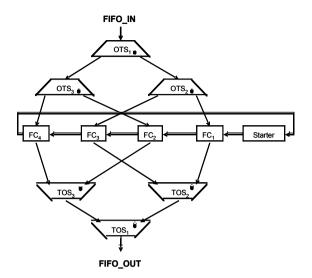

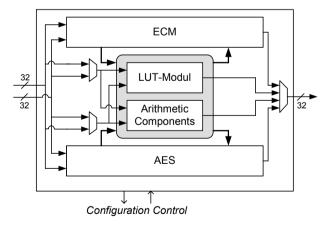

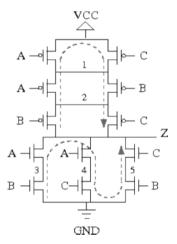

Figure 6 represents the DES core architecture, implementing a four-phase handshake protocol, using 1-to-N encoded data and balanced data-paths [2]. The architecture is composed of three iterative asynchronous loops synchronized through communicating channels. One loop for the ciphering data-path, the second for the key data-path and the last one for the control data-path which enables the control of the sixteen iterations of the algorithm.

For example let's apply the technique to the five grey blocks of figure 6. Each block has its own acknowledgement signal and the delay inserted in each acknowledgment signal can take four values. Therefore, there are 1024 possible delay values (n=1024). It means that (in terms of DPA resistance) the current peak variations corresponding to  $d_{xi}(t_i)$  will be divided by 1024.

Fig. 6. Asynchronous DES core architecture

# 5 Results and Analysis: Electrical simulations

Electrical simulations enable us to analyze the electrical behaviour of the design with high accuracy, i.e. without disturbing signal (noise). All electrical simulations are performed with *Nanosim* using the HCMOS9 design kit (0.13! m) from STMicroelectronics.

The architecture used for these electrical analysis implements one acknowledgement signal per block. However, for the needs of illustration only the acknowledgment signal of the inputs of the *SBOX1* is randomly delayed with 8 different delays. The defined selection function, used to implement the attack, is as follows:

#### $D(C_n, P_{\phi}K_0) = SBOX1(P_{\phi} \bigoplus K_0)$ with $n \in \{1, 2, 3, 4\}$

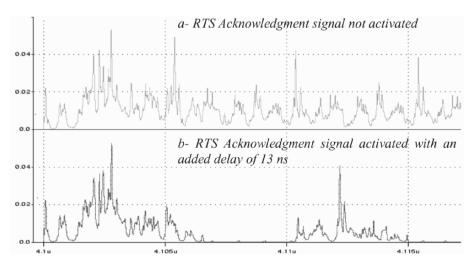

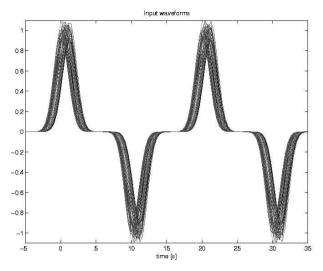

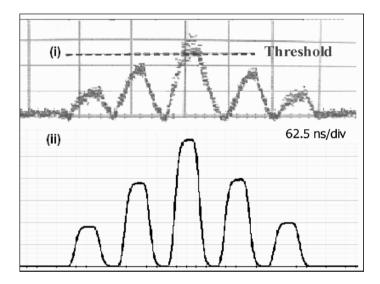

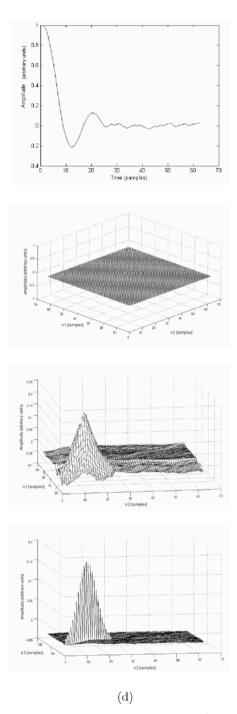

The DPA attack has been implemented on the four output bits of the *SBOX1* and on the first iteration of the DES algorithm using 64 plaintext inputs (N=64). Figure 7 shows the current profile of the first iteration when the RTS acknowledgment signal is activated and deactivated. When the delay of 13ns is used, the time required for processing an iteration (figure 7-b) corresponds to the time required to process 3 iterations without delays (figure 7-a). Hence the ciphering time is multiplied by a factor 3. This delay is chosen for the sake of illustration only. Given a level of DPA resistance, the delay can be strongly decreased in practice (down to a few nanoseconds with this technology) to reduce as much as possible the timing overhead as well as the hardware overhead caused by the application of the technique

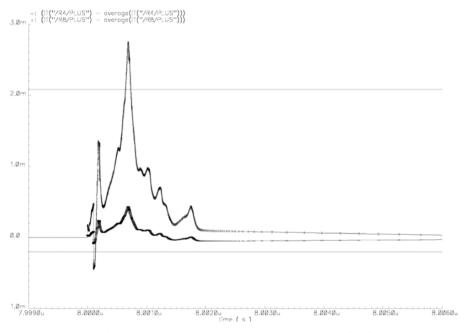

Fig. 7. Current profile of the DES QDI asynchronous architecture.

Only the first iterations are considered

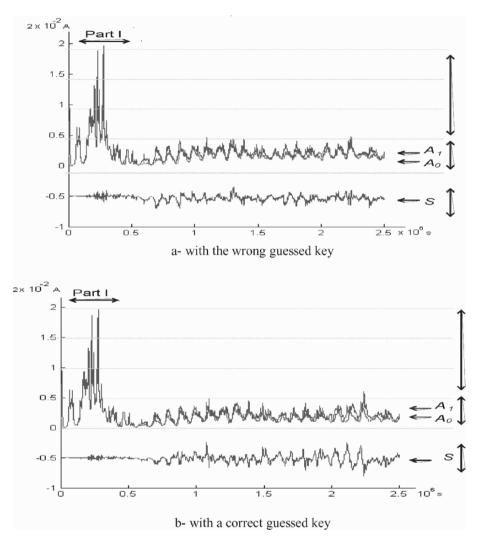

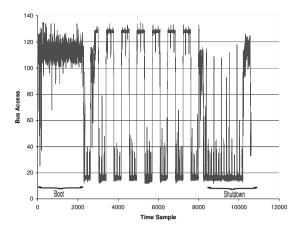

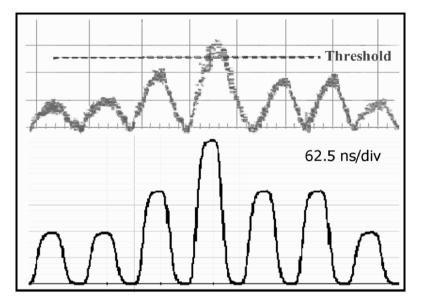

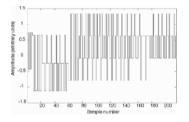

**Fig. 8.** Electrical signatures when performed DPA attack on bit 4 of the SBOX1. Only the first round is considered and computed using more than 2.100.000 point.

As the *SBOX1* has four output bits encoded in dual-rail, we have 8 data-paths (from outputs to inputs) which enable to compute 8 values of  $d_{xi}(t_j)$ . Let's recall that,  $d_{xi}(t_j)(d_{0i}(t_j);d_{1i}(t_j))$  corresponds to the amount of dissipated power when the attacked bit is processed at time  $t_i$ . For example, let's consider the output bit 4 of the *SBOX1*.

Contrary to a standard approach and due to the 8 delay shifts, the values  $d_{04}(t_j)$  and  $d_{14}(t_j)$  are processed 4 times instead of being processed 32 times, so that their weights are reduced by a factor 8 into sets  $S_1$  and  $S_0$ . Each of this set enables us to calculate the average currents  $A_0(t_j)$  and  $A_1(t_j)$ .

Figure 8 shows these average current profiles  $(A_0(t_j) \text{ and } A_1(t_j))$  which are used to compute the DPA bias signal  $(S(t_j))$ , also shown in figure 8.

Part I of these curves represent the first encryption operations in the first iteration (see figure 8). This part is not affected by the RTS acknowledgment signal which is only applied on *SBOX1*. In fact, before computing the *SBOX* function, the chip first computes IP, Expansion and Xor48 functions (figure 6), so that, in the first iteration, these functions, are not affected by the RTS acknowledgement signal of *SBOX1*. This explains why the amplitude of the average power curve starts decreasing after part I and it clearly illustrates the effect of the RTS signal on the power curves. This can of course be changed by activating the RTS acknowledgement signals of blocks IP, Expansion and/or Xor48.

In the considered example, 64  $PTI_i$  curves are used to implement the attack. In this case, obtaining the key bit from the DPA bias signal is impossible as shown in figure 8. Indeed, there is no relevant peak in the DPA current curves (figure 8-a and 8-b).

# 6 Conclusion

This paper presented a countermeasure against DPA based on randomly timeshifted acknowledgment signals of asynchronous QDI circuits. The efficiency of the countermeasure was first theoretically formalized and then demonstrated using electrical simulations. The technique principle was illustrated on a DES architecture.

Future works will be focused on the design and fabrication of a DES prototype implementing the RTS acknowledgement signals together with a random number generator.

## 7 References

- P. Kocher, J. Jaffe, B. Jun, "Differential Power Analysis," Advances in Cryptology - Crypto 99 Proceedings, Lecture Notes In Computer Science Vol. 1666, M. Wiener ed., Springer-Verlag, 1999.

- Simon Moore, Ross Anderson, Paul Cunningham, Robert Mullins, George Taylor, "Improving Smart Card Security using Self-timed Circuits", Eighth International Symposium on Asynchronous Circuits and systems (ASYNC2002). 8-11 April 2002. Manchester, U.K.

- L. A. Plana, P. A. Riocreux, W. J. Bainbridge, A. Bardsley, J. D. Garside and S. Temple, "SPA - A Synthesisable Amulet Core for Smartcard Applications", Proceedings of the Eighth International Symposium on Asynchronous Circuits and Systems (ASYNC 2002). Pages 201-210. Manchester, 8-11/04/2002. Published by the IEEE Computer Society.

- Jacques J. A Fournier, Simon Moore, Huiyun Li, Robert Mullins, and Gerorge Taylor, "Security Evalution of Asunchronous Circuits", CHES 2003, LNCS 2779, pp 137-151, 2003.

- F. Bouesse, M. Renaudin, B. Robisson, E Beigne, P.Y. Liardet, S. Prevosto, J. Sonzogni, "DPA on Quasi Delay Insensitive Asynchronous circuits: Concrete Results", To be published in XIX Conference on Design of Circuits and Integrated Systems Bordeaux, France, November 24-26, 2004.

- G.F. Bouesse, M. Renaudin, S. Dumont, F. Germain, « DPA on Quasi Delay Insensitive Asynchronous Circuits: Formalization and Improvement », DATE 2005. p. 424

- T. S. Messerges and E. A. Dabbish, R. H. Sloan, "Investigations of Power Analysis Attacks on Smartcards", USENIX Workshop on Smartcard Technology, Chicago, Illinois, USE, May 10-11, 1999.

- Marc Renaudin, "Asynchronous circuits and systems: a promising design alternative", Microelectronic for Telecommunications : managing high complexity and mobility" (MIGAS 2000), special issue of the Microelectronics-Engineering Journal, Elsevier Science, GUEST Editors : P; Senn, M. Renaudin, J, Boussey, Vol. 54, N° 1-2, December 2000, pp. 133-149.

- Viktor Fischer, M. Drutarovský, True Random Number Generator Embedded in Reconfigurable Hardware, In C. K. Koç, and C. Paar, (Eds.): Cryptographic Hardware and Embedded Systems (CHES 2002), Redwood Shore, USA, LNCS No. 2523, Springer, Berlin, Germany, ISBN 3-540-00409-2, pp. 415-430.

- 10. V. Fischer, M. Drutarovský, M. Šimka, N. Bochard, High Performance True Random Number Generator in Altera Stratix FPLDs, in J. Becker, M. Platzner, S. Vernalde (Eds.): "Field-Programmable Logic and Applications," 14th International Conference, FPL 2004, Antwerp, Belgium, August 30-September 1, 2004, LNCS 3203, Springer, Berlin, Germany, pp. 555-564.

# A Comparison of Layout Implementations of Pipelined and Non-Pipelined Signed Radix-4 Array Multiplier and Modified Booth Multiplier Architectures

Leonardo L. de Oliveira<sup>1</sup>, Cristiano Santos<sup>2</sup>, Daniel Ferrão<sup>2</sup>, Eduardo Costa<sup>3</sup>, José Monteiro<sup>4</sup>, João Baptista Martins<sup>1</sup>, Sergio Bampi<sup>2</sup>, Ricardo Reis<sup>2</sup> <sup>1</sup> Federal University of Santa Maria, PPGEE – GMICRO, Av. Roraima 1000, Camobi, 97105-900 Santa Maria - RS, Brazil, leonardo@mail.ufsm.br, batista@inf.ufsm.br WWW home page: http://www.ufsm.br/gmicro <sup>2</sup> Federal University of Rio Grande do Sul, PPGC – GME, Av. Bento Goncalves, 9500, Agronomia, 91501-970 Porto Alegre - RS, Brazil, {clsantos,dlferrao,bampi,reis}@inf.ufrgs.br WWW home page: http://www.inf.ufrgs.br/gme <sup>3</sup> Catolic University of Pelotas, Rua Félix da Cunha 412, 96010-000 Pelotas - RS, Brazil, ecosta@atlas.ucpel.tche.br WWW home page: http://www.ucpel.tche.br <sup>4</sup> INESC-ID/IST, Rua Alves Redol 9, 1000-029 Lisboa – Portugal, jcm@inesc-id.pt WWW home page: http://www.inesc-id.pt

**Abstract.** This paper presents performance comparisons between two multipliers architectures. The first architecture consists of a pure array multiplier that was modified to handle the sign bits in 2's complement and uses a radix-4 encoding to reduce the partial product lines. The second architecture implemented was the widely used Modified Booth multiplier. We describe a design methodology to physically implement these architectures in a pipelined and non-pipelined form, obtaining area, power consumption and delay results. Up to now only results at the logic level were presented in previous work. The performance of pipelined array architecture is compared with the pipelined Modified Booth. We compare the physical implementations in terms of area, power and delay. The results show that the new pipelined array multiplier can be significantly more efficient, with close to 16% power savings and 55% power savings when considering non-pipelined architectures.

De Oliveira, L.L., Santos, C., Ferrão, D., Costa, E., Monteiro, J., Martins, J.B., Bampi, S., Reis, R., 2007, in IFIP International Federation for Information Processing, Volume 240, VLSI-SoC: From Systems to Silicon, eds. Reis, R., Osseiran, A., Pfleiderer, H-J., (Boston: Springer), pp. 25–39.

# 1 Introduction

Multiplier modules are common to many DSP applications. The fastest types of multipliers are parallel multipliers. Among these, the Wallace multiplier [18] is among the fastest. However, they do not have such a regular structure as the conventional array [11] or Booth [13] multipliers. Hence, when layout regularity, high-performance and low power are primary concerns, Booth multipliers tend to be the primary choice [2], [7], [9], [13], [16].

In this paper, we present layout implementations for both the Modified Booth multiplier and the new array multiplier in non-pipelined and pipelined versions. The pipelined version of the radix-4 architecture was implemented in order to reduce both the critical path and useless signal transitions that are propagated through the array. This array architecture is extended for radix 2<sup>m</sup> encoding, which leads to a reduction of the number of partial lines, enabling a significant improvement in performance and power consumption.

We synthesize the multipliers by using an automatic synthesis tool, named TROPIC [15]. In order to compare the Modified Booth and the array architectures, both using radix-4, the ELDO – a spice simulator, part of the Mentor Graphics environment, was used. The results show that the new array multiplier is significantly more efficient, saving more than 50% in power consumption. This result is very close to the results reported in [4], obtained at the logic level using a switch-level simulator and 16% power savings considering pipelined versions.

The power reduction presented by the new array multiplier is mainly due to the lower logic depth, which has a big impact in the amount of glitching in the circuit. We should stress further that, in contrast to the architecture presented in [4], rasing the radix for the Booth architecture is a difficult task, thus not being able to leverage from the potential savings of higher radices.

This paper is organized as follows. In the next section we give an overview of relevant work related to our work. In section 3 we present a 2's complement binary multiplication. After that, Section 4 briefly describes the radix-4 array multiplier. The Modified Booth multiplier and their pipelined forms are described in Section 5. Section 6 describes the design methodology and how area, power and delay results are obtained. Comparisons between the radix-4 array multiplier architecture and the Modified Booth, for both switch level and electrical level are presented in Section 7. Finally, in Section 9 we conclude this paper, discussing the main contributions and future work.

# 2 Related Work

A substantial amount of research work has been put into developing efficient architectures for multipliers given their widespread use and complexity. Schemes such a bisection, Baugh Wooley and Hwang [9] propose the implementation of a 2's complement architecture, using repetitive modules with uniform interconnection patterns. However, an efficient VLSI realization is more difficult due to the irregular tree-array form used. The same non-regularity aspect is observed in [13], where a scheme of a multiplexer–based multiplier is presented. In [11] an improvement of

this technique is observed where the architecture has a more rectangular layout than [13].

The techniques described above have been applied to conventional array multipliers whose operation is performed bit by bit and some times the regularity of the multipliers is not preserved. More regular and suitable multiplier designs based on the Booth recoding technique have been proposed [7][2][16]. The main purpose of these designs is to increase the performance of the circuit by the reduction of the number of partial products. In the Modified Booth algorithm approximately half of the partial products that need added is used.

Although the Booth algorithm provides simplicity, it is sometimes difficult to design higher radices due to the complexity to pre-compute an increasing number of multiples of the multiplicand within the multiplier unit. In [7][16] high performance multipliers based on higher radices are proposed. However, these circuits have little regularity and no power savings are reported. Research work that directly targets power reduction by using higher radices for the Booth algorithm is presented in [2][10]. Area and power improvements are reported with a highly optimized encoding scheme ate the circuit level. At this level of abstraction some other works have applied complementary pass-transistor logic in their design in order to improve the Booth encoder and full adder circuits [9][13][14].

In our work, the improvement in power has the same principal source as the Booth architecture, the reduction of the partial product terms, while keeping the regularity of an array multiplier. We show that our architecture can be more naturally extended for higher radices using less logic levels and hence presenting much less spurious transitions. We present layout implementation of pipelined and nonpipelined versions of our multipliers.

# **3** Array Multipliers

In this section we describe how we derive the 2's complement binary multiplication. Consider two operands W-bits wide,  $A = \sum_{i=0}^{W-1} a_i 2^i$  and

$$B = \sum_{j=0}^{W-1} b_j 2^j$$

. We have that

$$A \times B = \sum_{j=0}^{W-1} A \cdot b_j 2^j$$

(1)

where in turn,

$$A \cdot b_j = \sum_{i=0}^{W-1} b_j \cdot a_i 2^i \tag{2}$$

A conventional array multiplier [3] translates this expression directly to hardware, where we have the W partial product rows from Equation 1, each made of W bit level products as in Equation 2, which can be arranged in a simply, very regular, array structure. Each bit product is simply an AND gate.

The conventional array multiplier is only applicable to unsigned operands. We are able to show that exactly the same architecture can be used on signed operands in 2's complement with very little changes.

2's complement is the most used encoding for signed operands. The most significant bit,  $a_{W-1}$ , is the sign bit. If the number A is positive, its representation is the same as for an unsigned number, simply A. If the number is negative, it is represented as  $2^{W} - A$ .

Conversely, the value of the operand can be computed as follows:

$$A = \begin{cases} A & , & a_{W-1} = 0 \\ A - 2^{W} & , & a_{W-1} = 1 \end{cases}$$

(3)

We make the following observation that enables us simplify our architecture. Let us define  $A' = \sum_{i=0}^{W-2} a_i 2^i$ , an unsigned value. For positive numbers,  $a_{W-1} = 0$ , hence the value represented by A is A'. For negative numbers,  $a_{W-1} = 1$ , hence this value is  $A - 2^W = (2^{W-1} + A') - 2^W = A' - 2^{W-1}$ . Then equation 3 becomes:

$$A = \begin{cases} A' & , \quad a_{W-1} = 0\\ A' - 2^{W-1} & , \quad a_{W-1} = 1 \end{cases}$$

(4)

or simply  $A = A' - a_{W-1} 2^{W-1}$

or simply  $A = A' - a_{W-1} 2^{W-1}$

What Equation 4 tell us is that the multiplication of two operands in 2's complement can be performed as an unsigned multiplication for  $(W-1)^2$  of the bit products. Let us consider the 4 possible scenarios for  $A \times B$ :

$$A > 0, B > 0: A' \times B'$$

$$A > 0, B < 0: A' \times B' - A'2^{W-1}$$

$$A < 0, B > 0: A' \times B' - \sum_{j=0}^{W-1} b_j 2^{W-1+j}$$

$$A < 0, B < 0: A' \times B' - A'2^{W-1} - \sum_{j=0}^{W-1} b_j 2^{W-1+j}$$

which can be reduced to

$$(5)$$

which can be reduced to

$$A \times B = A' \times B' - b_{W-1} A' 2^{W-1} - a_{W-1} \sum_{j=0}^{W-1} b_j 2^{W-1+j}$$

(6)

The form of Equation 6 highlights:

- from the first term, that the *W-1* least significant bits A and B can be treated exactly as an unsigned array multiplier;

- from the second term, that the last row of the multiplier is either nonexistent (B>0) or a subtracter of A' shifted by W-1 bits (B<0);</li>

- from the third term, that, at each partial product line, the most significant bit is either 0 (A>0) or -1 (A<0).

Consider now  $A' = \sum_{i=0}^{\frac{W}{m}-2} a_i 2^{im}$ , where  $a_i$  is a m-bit digit. For positive numbers, the value represented by A is A' as before. For negative numbers, this

value is  $A - 2^{W} = a_{\frac{W}{m}-1} 2^{W-m} + A' - 2^{W} = A' - a_{\frac{W}{m}-1} 2^{W-m}$ , since  $a_{\frac{W}{m}-1} 2^{W-m} - 2^{W}$ is the 2's complement of  $a_{\frac{W}{m}-1} 2^{W-m}$ . Then we have:

$$A = \begin{cases} A' & , & a_{W-1} = 0\\ A' - a_{\frac{W}{m-1}} 2^{W-m} & , & a_{W-1} = 1 \end{cases}$$

(7)

or simply

$$A = A' - a_{W-1} a_{\frac{W}{m}-1} 2^{W-m}$$

(8)

Using analogous observations as made for the binary case, from Equation 8 we can write:

$$A \times B = A' \times B' - A' b_{W-1} b_{\frac{W}{m-1}} 2^{W-m} - a_{W-1} a_{\frac{W}{m-1}} \sum_{j=0}^{\frac{m}{m-1}} b_j 2^{W-m+j}$$

(9)

# 4 Radix-2<sup>m</sup> Array Multiplier

In this section, we summarize the methodology of [5] for the generation of regular structures for arithmetic operators using signed radix-2<sup>m</sup> representation and extend it into a pipelined version [6].

For the operation of a radix- $2^m$  multiplication, the operands are split into groups of *m* bits. Each of these groups can be seen as representing a digit in a radix- $2^m$ . Hence, the radix- $2^m$  multiplier architecture follows the basic multiplication operation of numbers represented in radix- $2^m$ . The radix- $2^m$  operation in 2's complement representation is given by Equation 10.

$$R \times Y = R' \times Y' - R' y_{W-1} y_{\frac{W}{m-1}} 2^{W-m} - r_{W-1} r_{\frac{W}{m-1}} \sum_{j=0}^{\frac{m}{m-1}} y_j 2^{W-m+j}$$

(10)

where R and Y are two operands W-bits wide;  $r_{W-1}$  is the most significant bit (is the

sign bit); and

$$R' = \sum_{i=0}^{W-2} r_i 2^i$$

.

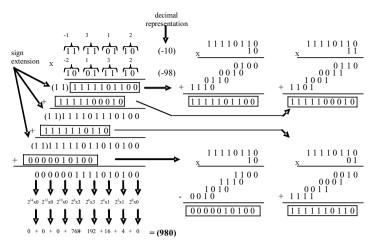

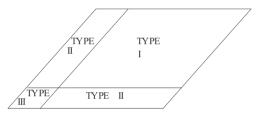

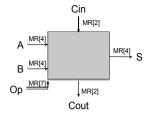

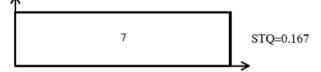

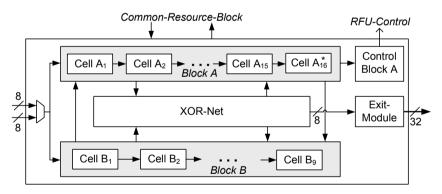

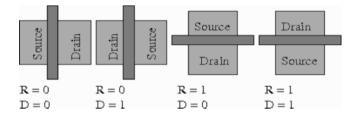

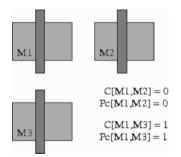

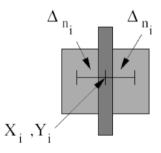

This operation is illustrated in Fig. 1. For the *W*-*m* least significant bits of the operands unsigned multiplication can be used. The partial product modules at the left and bottom of the array need to be different to handle the sign of the operands.

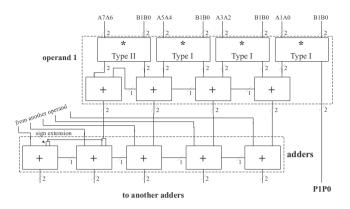

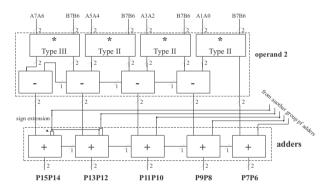

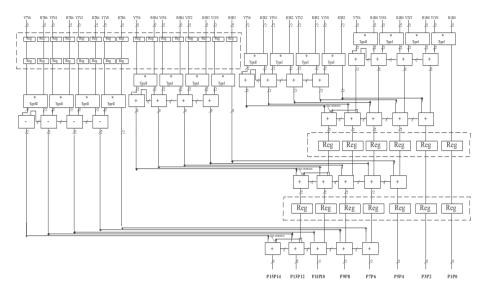

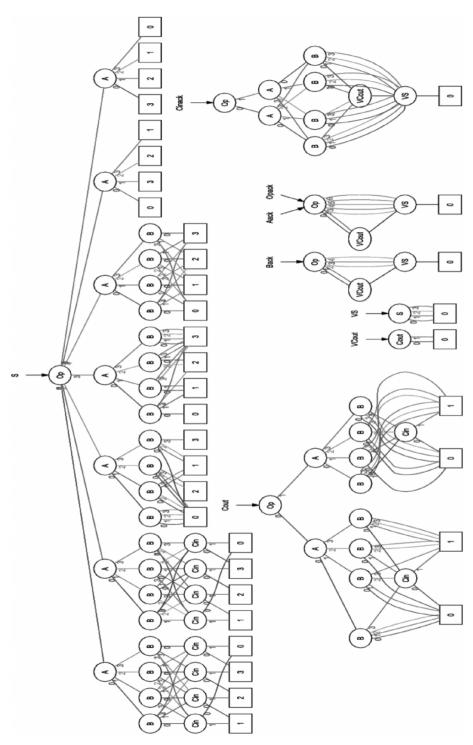

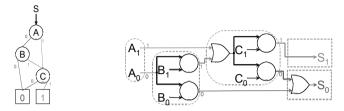

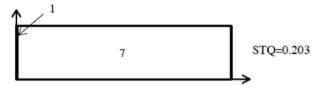

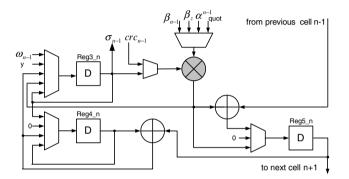

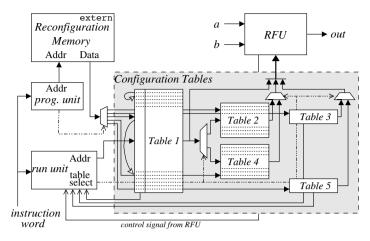

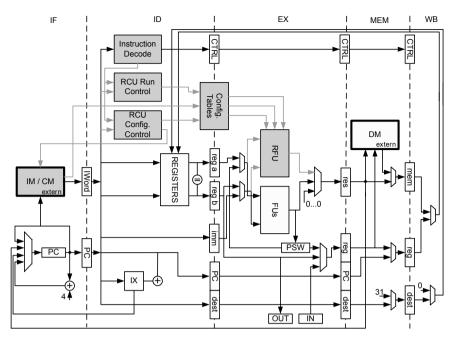

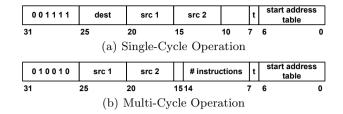

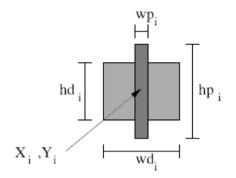

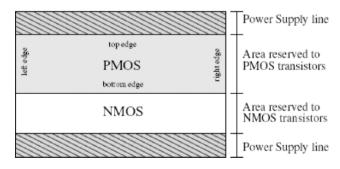

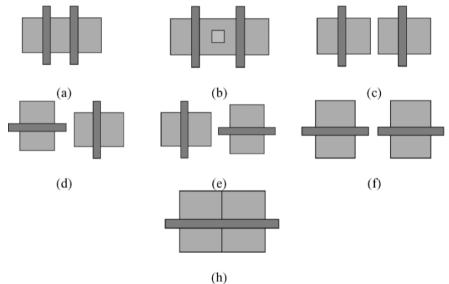

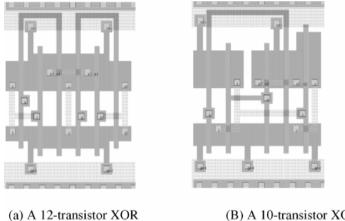

For this architecture, three types of modules are needed, as shown in Fig. 2. Type I are the unsigned modules. Type II modules handle the *m*-bit partial product of an unsigned value with a 2's complement value. Finally, Type III are modules that operate on two signed values. Only one Type III module is required for any type of multiplier, whereas  $2\frac{W}{m} - 2$  Type II modules and  $(\frac{W}{m} - 1)^2$  Type I modules are needed. Fig. 6 shows an example of an 8-bit wide 2's pipelined complement radix-4 array multiplier.

Fig. 1. Example of a 2's complement 8-bit wide radix-4 multiplication

Fig. 2. General structure for a 2's complement radix-2m multiplier

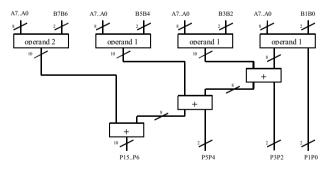

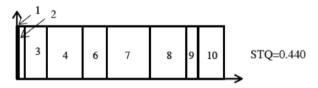

We present a summarized example for W=8 bit wide operands using radix-4 (m=2) in Fig. 3.

Fig. 3. 8-bit wide 2's complement Binary array multiplier m=2

Figure 4 and Figure 5 show the structure of operands 1 and 2, their inputs and outputs and nearest connections between them and the blocks of adders. In additional they show the sign extension that has been used in operands 1 and 2.

Fig. 4. Operand 1 and connections to first line of adders showing the sign extension

Fig. 5. Operand 2 and connections to third line of adders showing the sign extension

#### 4.1 Pipelined Array Multiplier

Glitches are unwanted switching activities that occur before a signal settles to its intended value. Each clock edge changes the inputs to the combinatorial logic between registers and every node has a different delay from different inputs, which change their state several times before settling down. Glitches on a node are dependent on the logic depth to that node, i.e. the number of logic gates from the node to the primary inputs (or sequential elements). The deeper and wider the logic behind a node, the more it glitches. These glitches can be reduced by reducing the depth of logic levels

The regularity of this array architecture makes it suitable for the application of other power reducing techniques. A pipelined version was constructed in order to reduce the critical path and useless signal transitions that are propagated through the array. The doted lines in Fig. 6 show the pipelined version of the radix-4 array multiplier for 8-bit operands. As can be observed, the advantage of the layered structure of the array was taken into account and two layers of registers were introduced. Thus, 3 clock cycles are necessary to perform the computation considering 8-bit architectures.

Fig. 6. Example of an 8-bit wide 2's complement radix-4 array multiplier

### 5 Modified Booth multiplier

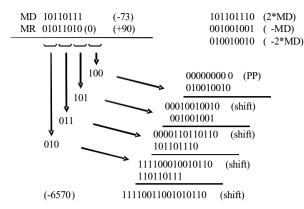

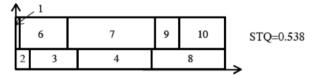

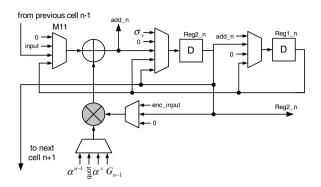

The radix-4 Booth's algorithm (also called Modified Booth) has been presented in [5]. In this architecture it is possible to reduce the number of partial products by encoding the two's complement multiplier. In the circuit the control signals (0, +Y, +2Y, -Y and -2Y) are generated from the multiplier operand Y for each 3-bit group, as shown in the example of Fig. 7, for an 8-bit wide operation. A multiplexer produces the partial product according to the encoded control signal.

Common to both architectures is that, at each step of the algorithm, two bits are processed. However, the basic Booth cells are not simple adders as in the array multiplier, but must perform addition-subtraction-no operation and controlled left-shift of the bits of the multiplicand. Fig. 8, shows an example of an 8-bit modified Booth architecture.

#### 5.1 Pipelined Modified Booth Multiplier

A pipelined Modified Booth by introducing registers along the layers of the array was implemented in and it is presented in Fig. 8. As it can be observed in this figure, there are two layers of registers along the array as in the binary array multiplier with m=2. Again, 3 clock cycles are required to compute the final result in the 8-bit architecture and six cycles to the 16-bit one. Moreover, common to both architectures is that the registers are inserted at the output of the adders which are responsible for adding the partial product terms. However, in the Booth multiplier it is also necessary to introduce registers in the output of the encoders to perform the correct operation of each clock cycle as shown in Fig. 8.

Fig. 7. Example of an 8-bit multiplication with Modified Booth algorithm

Fig. 8. 8-bit pipelined modified Booth architecture

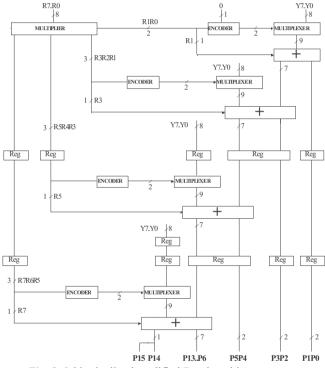

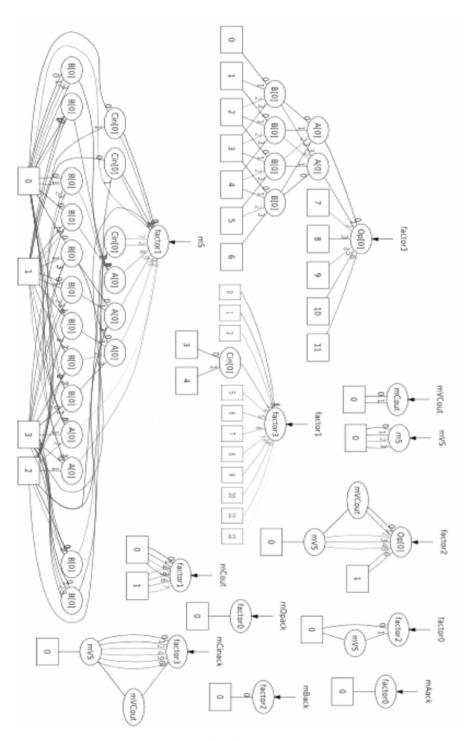

## 6 Design Methodology

Fig. 9 shows the design flow used in the physical implementation of the multipliers. Two methodologies are presented: our methodology (black), and the methodology used in [7] and [8] with the SIS environment (gray). The multipliers were originally described in BLIF (Berkeley Logic Interchange Format). Thus, these BLIF files are used as input of the design flow, as can be observed in Fig. 9.

In [5] and [6], the performance of the multipliers was evaluated only in a logic level. The SIS [17] tool was used to synthesize and estimate area and delay of the multipliers while power consumption was estimated using the switch-level simulator SLS [8].

Fig. 9. Design tools for synthesis and performance estimation

In this work, the TROPIC tool was used for the physical synthesis of the implemented multipliers. This tool uses a spice like format (*sim*) as input and performs a library-free automatic layout generation of the circuit regarding the design rules of the target technology. TROPIC gives the total area occupied by the layout and the number of transistors of the synthesized circuits. Before the layout synthesis of the circuits, it is necessary to set the size of the transistors and the number of rows. This last parameter is useful to set the aspect ratio width/height.

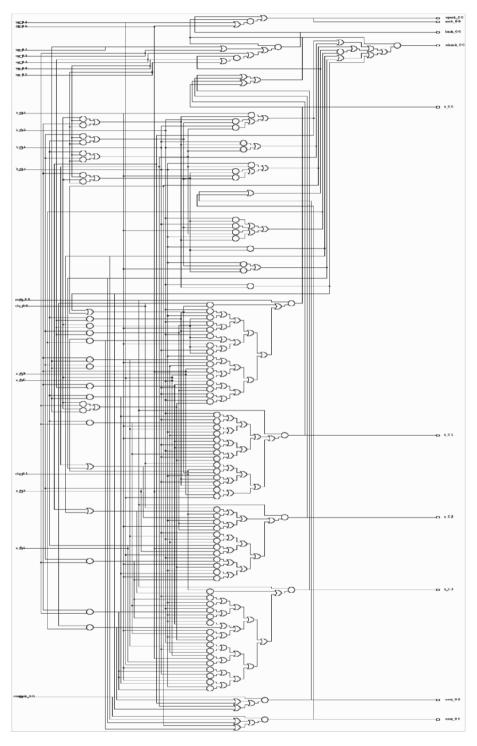

Since the TROPIC tool generates the widely used *cif* format, the resulting circuit layout can be visualized with Mentor Graphics IC Station tool. Fig. 10 shows the layout for the 8-bit array multiplier, which was generated automatically by TROPIC tool. Once the *cif* file is generated, an electrical extraction can be performed using the TROPIC tool.

The extracted SPICE netlists were simulated using the ELDO electrical simulator in order to obtain power estimation at the back-annotated electrical level. This simulator is part of the Mentor Graphics environment for power estimation. The same set of input vectors used in [4] and [5] for power estimation was converted from SLS to SPICE format and then used for transient analysis.

The timing analysis tool PrimeTime [12] was used to estimate the critical delay of the circuits. PrimeTime is able to perform both static and functional timing analysis. Static timing analysis (STA) is the standard approach used for delay estimation in the current designs complexity. The main issue of this approach is that logic information about the cells of the circuit is not considered during the critical delay search. At the same time that this issue makes the delay estimation faster, it can make STA suffers from the false path syndrome. In order to avoid this false path syndrome, the designer must report all timing exceptions of the circuit to the STA tool, and it can be a very hard task.

Another way to avoid false paths during delay estimation is using functional timing analysis (FTA). FTA performs the critical delay search taking into account information about the logic cells of the circuit. So, paths that can not propagate a

transition are not considered and the critical delay will be the delay of the longest sensitizable path. Primetime uses the Exact Floating Mode sensitization criterion during the critical path search. This sensitization criterion considers both logic and timing information of the cells during the path sensitization.

Fig. 10. Layout of an 8-bit array multiplier generated automatically by TROPIC

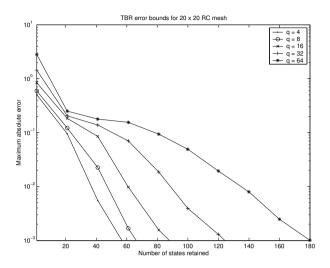

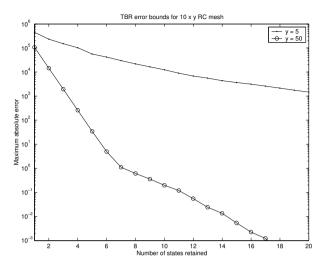

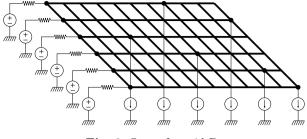

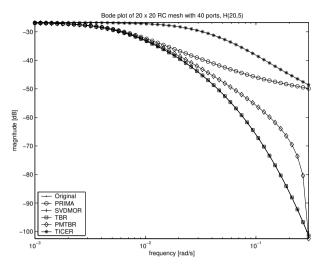

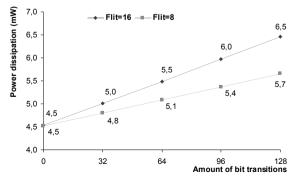

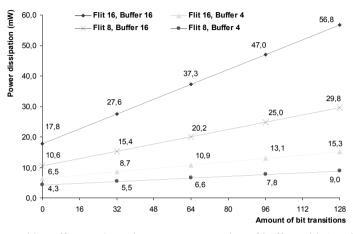

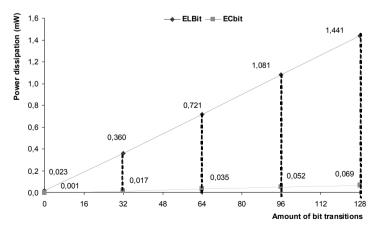

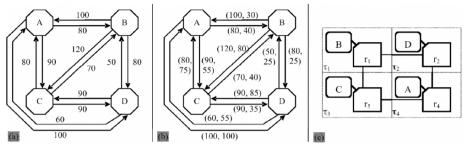

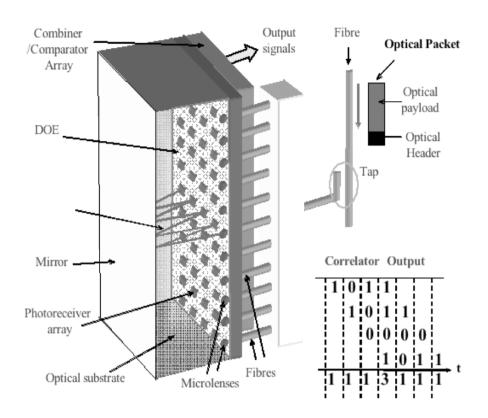

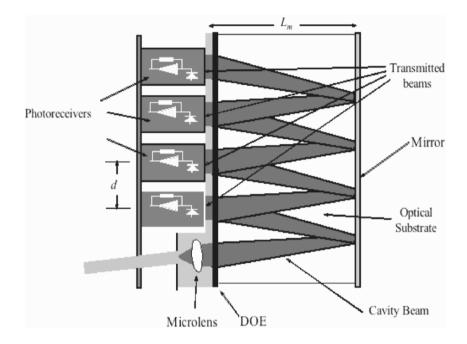

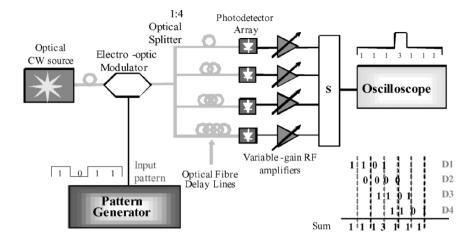

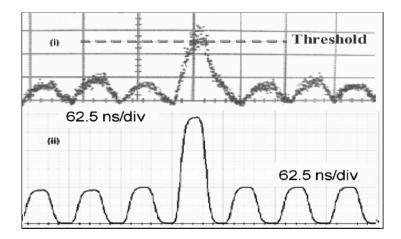

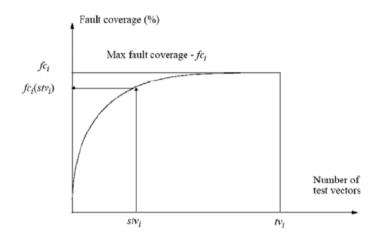

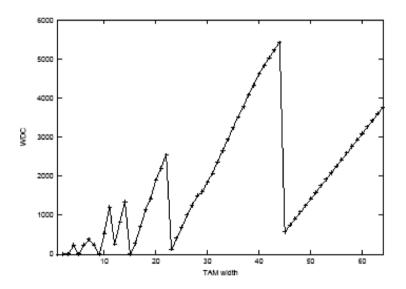

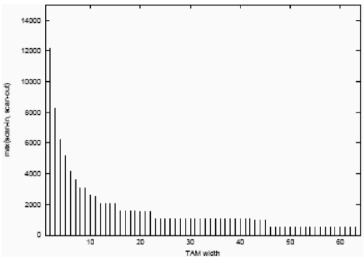

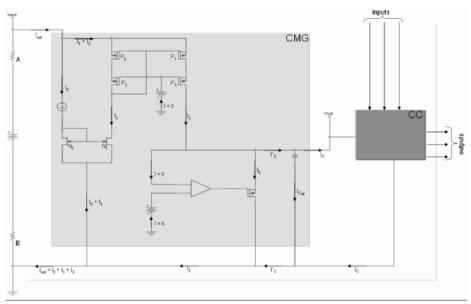

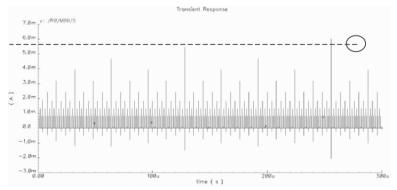

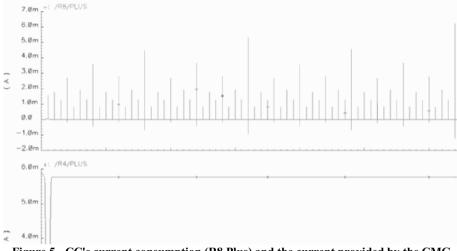

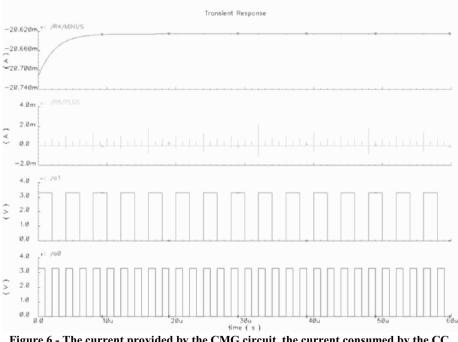

# 7 Performance Comparisons